Digital VLSI SoC

Design and Planning

(Duration - 2 Weeks)

Overview

Do you find yourself asking, “What are these obstacles?” “How does this intricate process work?” “Could I actually create my own chip?” If these questions ignite your curiosity and you’re passionate about delving into the ASIC design flow, your adventure starts here!

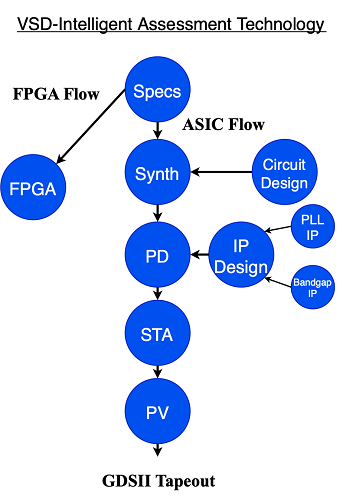

We’re excited to introduce a game-changer: the Google-Sky Water collaboration has unveiled the first open source, manufacturable 130nm process design kit (pdk). This innovation transcends the boundaries of academic research and small-scale projects, propelling the open-source EDA world into a new dimension.

Coupled with the inception of Openlane flow, a fully automated RTL2GDSII process, we’re closer than ever to realizing the dream of “an IC for everyone.” Get ready for the ultimate workshop on SoC design planning using the revolutionary Google-SkyWater 130nm process node within the OpenLANE flow.

This workshop is your gateway to:

- Crafting and characterizing standard cells.

- Gaining practical experience in the Physical Design domain.

- Generating a complete GDSII from an RTL netlist.

- Diving into and enriching the open-source EDA landscape.

Seize this unparalleled opportunity to transform your passion into expertise!

Testimonials

Read More

Read More

Read More

Read More

Read More

5 compelling reasons to join this workshop

- VSD Product-Based Skilling Advantage

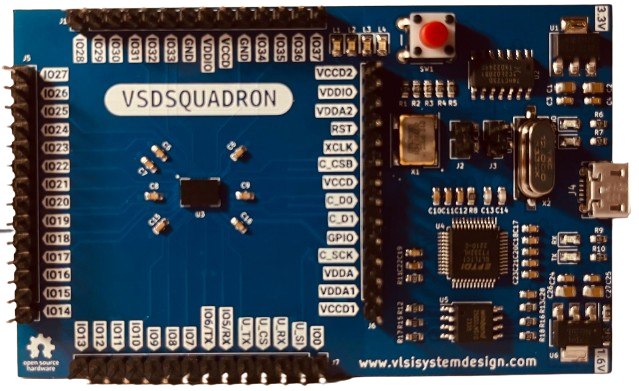

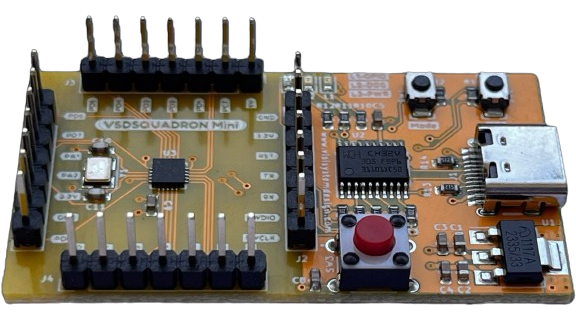

- RISC-V chips and VSDSquadron board built by VSD Student community

- Researchers and hobbyists across 153 countries have tested and used it

- Get access to 60+ VSD inhouse IPs built by VSD Student community

- Chip Tapeout-Oriented Approach using VSD RTL2GDS Flow

- VSDemphasizes chip tapeout

- Focus on real-life scenarios that culminate in tapeout

- Offer more practical experience.

- Zero Fees for Tools

- EDA toolchain is open source

- Lifetime access with unlimited licenses

- Continue learning and designing even after the program concludes

- Career Opportunities

- Industry recognition for participants who have experience in chip tapeout

- Understand how Time-to-market is crucial in this field

- Opportunity to work directly on advanced analog, mixed-signal and RISC-V projects

- Cloud-Based Flexibility

- Self-paced learning

- Simple login to week's lectures and labs

- 24/7 Slack channel with over 150 teaching assistants

Curriculum

- Introduction to open-source EDA tools and 130nm PDKs

- Floorplanning and Standard cell design

- Designing and Characterizing a Library Cell

- Pre-Layout Timing Analysis and Clock Tree Synthesis

- The Final Leap: From RTL2GDS

Join us for this transformative journey and turn your fascination into tangible skills in the ever-evolving world of IC design!

Tools

- Yosys Synthesis Suite

- OpenLANE RTL2GDS digital design suite

- NGSpice for Characterization

- Magic for Layout and Floor planning

- OpenSTA for Static timing analysis

Lab Exercises

- RISC-V core synthesis

- ASIC design flow

- CMOS transient analysis

- Static timing analysis

- Layout and characterization

Projects

- RISC-V based core Picorv32 implementation and characterization

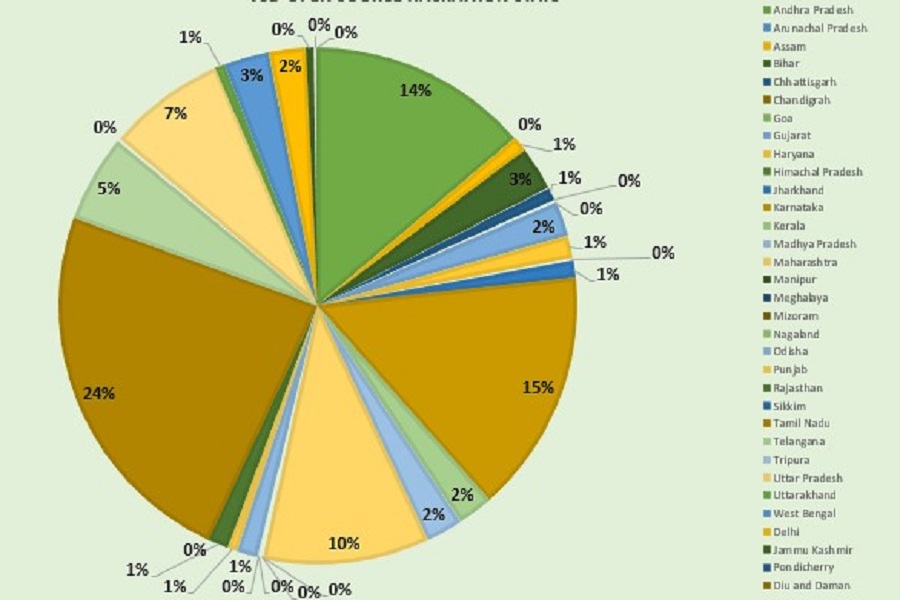

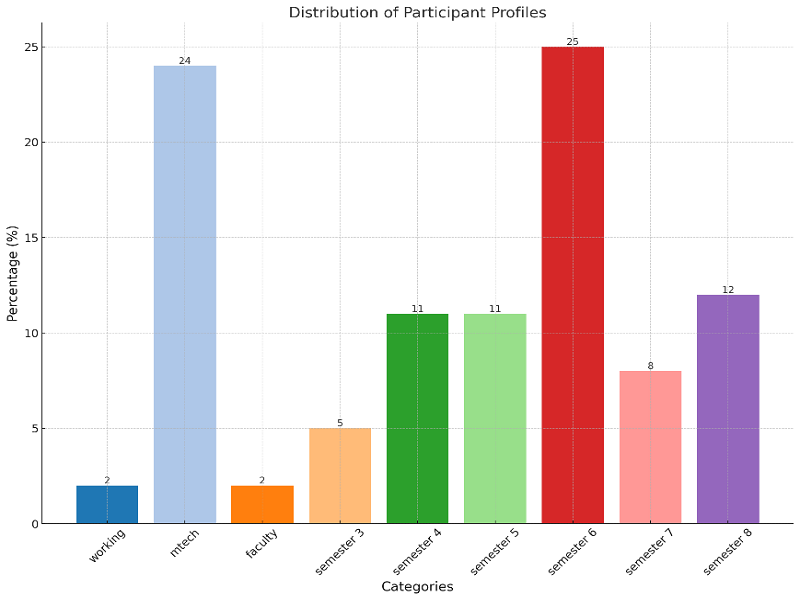

VSD Participants Profile

Delivery Mode

- Easy-to-access labs, available through a virtual box image

- Insightful Lectures on an Innovative VSD-IAT LMS Platform

- Round-the-Clock Q&A Support on Slack

- Daily Check-in Calls for Direct Interaction

Eligibility

Fresher or recently graduated or experienced professionals looking to brush fundamentals.

Atleast BE/BTech/ME/MTech or equivalent.

About VSD

Online Beginner Course

RTL GDSII VSD-IAT Workshop

VSD Community Based Silicon Tape Out

Analog & Mixed Signal IPs

VSDOpen Online Conference

Unique Global students

VSD Hackathon Participants

VSDSquadron Educational and Dev Kit

Over the past decade, VSD has made remarkable strides in the open-source semiconductor domain. Our journey includes the development of comprehensive training content, empowering students to design silicon-grade IP/SoC. Notably, we’ve successfully guided these projects through the tapeout cycle via the Google open shuttle program. This achievement is a testament to our commitment to hands-on, practical education.

At VSD, our role extends beyond traditional education. While we didn’t invent EDA tools or design flows, we’ve made them accessible to a wider community. Our mentorship has been instrumental in the development of over 50+ Analog/Digital IPs and solutions. Impressively, 20+ of these have successfully transitioned from concept to Silicon – a clear indicator of our effective approach and the high quality of work produced under our guidance.

We pride ourselves on fostering a community-based revolution in the Semiconductor Industry. By democratizing access to advanced tools and knowledge, VSD is not just educating individuals; we are building a community of innovators poised to lead the next wave of advancements in the semiconductor sector. With VSD, the future of VLSI Design is not just being written; it’s being rewritten by a passionate and empowered community.

Instructor Profile

Kunal Ghosh Kunal Ghosh, the visionary co-founder of VLSI System Design (VSD) Corp. Pvt. Ltd., stands at the forefront of online open-source EDA and hardware design education, particularly in the realm of RISC-V.

With a portfolio of 50 top-tier VLSI online courses, Kunal has enriched the learning journey of over 90,000 students across 153 countries. His expertise extends beyond training; he’s actively involved in pioneering open-source projects and design collaborations with esteemed institutions like IIT Madras, IIT Bombay, IIT Guwahati and IIT Hyderabad.

His current focus is on crafting high-quality open-source Analog/Digital IPs, a groundbreaking endeavor in open-source hardware design. Kunal’s rich industry experience includes roles at Qualcomm and Cadence, specializing in SoC design. He holds a master’s degree from IIT Bombay, where he specialized in VLSI & Nano-electronics, with a focus on sub-100nm Electron Beam Lithography Optimization techniques.

Kunal Ghosh Kunal Ghosh, the visionary co-founder of VLSI System Design (VSD) Corp. Pvt. Ltd., stands at the forefront of online open-source EDA and hardware design education, particularly in the realm of RISC-V.

With a portfolio of 50 top-tier VLSI online courses, Kunal has enriched the learning journey of over 90,000 students across 153 countries. His expertise extends beyond training; he’s actively involved in pioneering open-source projects and design collaborations with esteemed institutions like IIT Madras, IIT Bombay, IIT Guwahati and IIT Hyderabad.

His current focus is on crafting high-quality open-source Analog/Digital IPs, a groundbreaking endeavor in open-source hardware design. Kunal’s rich industry experience includes roles at Qualcomm and Cadence, specializing in SoC design. He holds a master’s degree from IIT Bombay, where he specialized in VLSI & Nano-electronics, with a focus on sub-100nm Electron Beam Lithography Optimization techniques. Timothy Edwards, the mastermind behind Opencircuitdesign.com and the Senior Vice President at Efabless, is a seasoned Analog VLSI designer with over 27 years of dedication to developing open-source EDA tools.

Timothy Edwards, the mastermind behind Opencircuitdesign.com and the Senior Vice President at Efabless, is a seasoned Analog VLSI designer with over 27 years of dedication to developing open-source EDA tools. His career journey has taken him through notable organizations such as Johns Hopkins Applied Physics Lab, startups MultiGiG, and Analog Devices. Timothy is the brain behind renowned open-source EDA software tools like Magic, Qflow, Netgen, and Xcircuit.

Professor Mohammed Shalan of the American University in Cairo is not only an academic but also a trailblazer in the field of digital ASIC/FPGA design, evidenced by his founding of CloudV.io and Fault.

Professor Mohammed Shalan of the American University in Cairo is not only an academic but also a trailblazer in the field of digital ASIC/FPGA design, evidenced by his founding of CloudV.io and Fault. His professional repertoire includes roles in embedded systems architecture for the automotive and mobile sectors at Mentor Graphics, as well as positions at MindSpeed, Freescale, and as a SoC consultant. Mohammed is a patent holder in Power Profiling and Optimization for Embedded System Design.

FAQ

What's the cost to register?

We've set a special discounted fee of INR 999 (INR7000). Our aim is to make Open-source EDA tools and PDKs accessible for various purposes such as college projects, PhD research, semester lectures, and keeping up with industry trends.

Can I participate according to my schedule?

Absolutely! The workshop is hosted on the VSD-IAT cloud platform, offering flexibility to log in at your convenience. The platform is accessible 24 hours a day during the two weeks duration of the workshop.

I'm a second-year engineering student. Is this workshop suitable for me?

Definitely! We welcome learners of all ages and backgrounds. Our previous RISC-V workshop included students as young as those in 8th grade. This workshop, while advanced in title, starts with the basics to ensure a solid foundational understanding.

Can experienced system designers join to refresh their knowledge?

This workshop is primarily designed for newcomers to the field of VLSI. However, experienced professionals interested in sharing their expertise with students are more than welcome to join.

Will I have access to the workshop content after it ends?

Yes, you will receive lifetime access to all lab files. However, access to the videos and the VSD-IAT platform will end with the workshop.

Do I need to install any software for the labs?

No, all labs will be conducted on the VSD-IAT cloud platform using a Linux Terminal with all necessary tools pre-installed. Post-workshop, we will provide scripts for you to install these tools on your own computer for further practice and revision.

How are the labs distributed for this workshop?

Labs will be shared via a virtual box image. You'll receive detailed instructions on accessing and using this image a day before the workshop starts.

What platform is used for the lectures?

Lectures will be delivered through the VSD-IAT LMS platform. This platform allows you to access course materials and interact with the content at your own pace.

Is there support available during the workshop?

Yes, our instructors and Teaching Assistants are available 24/7 on Slack throughout the 14-day workshop to answer questions, provide clarifications, and help.

Is there a specific time for addressing urgent issues?

Indeed, there's a daily one-hour sync-up call during the workshop. This is a valuable time for discussing any immediate issues, challenges, and for receiving direct guidance from instructors and TAs.

Is the workshop flexible for asynchronous participation?

Yes, the workshop is hosted on a cloud-based platform, allowing you to access materials and complete tasks at your convenience, ensuring flexibility in your learning schedule.

Boards

Registration Fee

Digital VLSI SoC-

11 -24 Dec 2024

Next Cohort will start in

Media Coverage

VSD Team interview taken by DD News at SEMICON India 2024

RISC-V Roadshow on SHAKTI Ideology

VSDSquadron was launched by Prof. V. Kamakoti, Director of IIT Madras

Innovation & Education Unite

VSD Launches VSDSquadron In Collaboration With IIT Madras & DIR-V

Unleashing VLSI

Job Roles, Convergence With Embedded Systems, and Startups

Semicon India Future Skills by IESA

VSD showcased at Semicon India 2023

Puthiya Thalaimurai

VSDSquadron Educational board on Tamil News channel

NIT Jamshedpur

5 Day Workshop on VLSI Design Flow using RISCV and EDA Tools

Sahyadri College

Karnataka VLSI roadshow at Sahyadri College, Mangalore